# 3.3.4 Configuration - Slow Control Interface

All configuration resources of the Trigger/Clock distribution tree are VME memory mapped. Therefore configuration and initialization can be performed by any processor in VME. It is assumed that the Slow-Control and Experiment-Control systems are able to call C-routines on a VME CPU. The arguments of the various initialization and maintenance routines have to be supplied and maintained by the calling shell. The following C-functions will be supplied:

- int reset (int detectorID)

- int configure (int detectorID, char \*config\_tag)

- int read\_config (int detectorID, char \*config\_tag)

All the listed functions return NULL on success and the error code in case of an error. The argument *detectorID* will be used to address the TCD module in the VME address space. The argument *config\_tag* is the header of a human readable ASCII file containing all TCD configuration information. It will be also passed to the appropriate mezzanine configuration routines.

Note: These are routines that will call the appropriate functions for the mezzanine boards. The mezzanine boards, however, are detector specific and require detector specific handling. Therefore the mezzanine specific routines have to be supplied by the group developing the mezzanine board itself. The shell routines listed above will decode the detector ID and call the following functions, where XXX stands for the appropriate detector acronym (capitalized):

- int XXX\_reset (void \* mezzanine\_base\_address)

- int XXX\_configure (void \* mezzanine\_base\_address, char \*config\_tag)

- int XXX\_read\_config (void \* mezzanine\_base\_address, char \*config\_tag)

Trigger/Clock drivers are allowed to use only power from the P1 and P3 back-plane. The Trigger/Clock fan-out boards use only the P2 power pins. The P2 back-plane will have an individual fuse that will prevent the back-plane from burning upon a power shortcut due to bent connector pins. This is possible because the fan-out boards will not need a lot of power.

There has to be a commercial module in the crate that allows initialization of the Trigger/Clock drivers. This module may use both the P1 and P2 power pins. Therefore, there will be two slots in the Trigger/Clock crate where the P1 and P2 power pins are connected. This crate will have correspondingly a 2 slot and a 19 slot P2 back-plane. These back-planes will be connected except for the power pins forming a virtual 21-slot VME P1/P2 back-plane. Such back-plane bridges with decoupled power pins are commercially available

TABLE 13. The pin assignment of the TCD fan-out back plane

| pin | signal (P3) | (VSB)  | pin | signal (P3) | (VSB)  |

|-----|-------------|--------|-----|-------------|--------|

| A01 | C0RHIC      | AD00   | C01 | C1RHIC      | AD01   |

| A02 | C0D0        | AD02   | C02 | C1D0        | AD03   |

| A03 | C0D1        | AD04   | C03 | C1D1        | AD05   |

| A04 | C0D2        | AD06   | C04 | C1D2        | AD07   |

| A05 | C0D3        | AD08   | C05 | C1D3        | AD09   |

| A06 | C0DCLK      | AD10   | C06 | C1DCLK      | AD11   |

| A07 | C0CLK1      | AD12   | C07 | C1CLK1      | AD13   |

| A08 | C0CLK2      | AD14   | C08 | C1CLK2      | AD15   |

| C28 | C0BUSY      | ASACK0 | C27 | C1BUSY      | ASACK1 |

| A32 | C0STATUS    | BREQ   | C31 | C1STATUS    | BUSY   |

|     |             |        |     |             |        |

| A09 | C2RHIC      | AD16   | C09 | C3RHIC      | AD17   |

| A10 | C2D0        | AD18   | C10 | C3D0        | AD19   |

| A11 | C2D1        | AD20   | C11 | C3D1        | AD21   |

| A12 | C2D2        | AD22   | C12 | C3D2        | AD23   |

| A13 | C2D3        | AD24   | C13 | C3D3        | AD25   |

| A14 | C2DCLK      | AD26   | C14 | C3CLK       | AD27   |

| A15 | C2CLK1      | AD28   | C15 | C3CLK1      | AD29   |

| A16 | C2CLK2      | AD30   | C16 | C3CLK2      | AD31   |

| C25 | C2BUSY      | ACK    | A24 | C3BUSY      | ERR    |

| C29 | C2STATUS    | CACHE  | C30 | C3STATUS    | WAIT   |

The DAQ command word and trigger token bypass the Trigger/Clock mezzanine board in order to save connector pins.

The 4-bit trigger command word is sent through the Trigger/Clock mezzanine in order to allow to intercept pulser triggers. This allows one pulser signal to result in a sequence of pulser trigger commands being sent to the front-end. During such a sequence the mezzanine board will assert the detector dead time. However, there are trigger commands that may still be broadcast that involve the busy detector, like L1 and L2 accepts or aborts of earlier events. Therefore, a trigger command FIFO is implemented on the Trigger/Clock Driver module (refer to figure 1) which absorbs and delays these commands during a pulser sequence. The control outputs instruct the sequencer to either transmit the trigger token driven by the mezzanine card or to distribute the latest trigger command.

**TABLE 12.** The control signals are defined as follows:

control[1:0]:

0 transmit the trigger command defined by the mezzanine board use the DAQ command and trigger token from FiFo

1 like above but use trigger command from mezzanine card

2 send out trigger command from mezzanine card

use the DAQ command and trigger token of the previous valid command

3 send out trigger command from mezzanine card

set DAQ command and trigger token to 0

control[2]: reserved

Table 12 shows the CMC P11 and P12 pin assignment. All signals are 5V TTL signals. There is no support for 3.3V logic. The connector P12 has only configuration signals connected. This allows Trigger/Clock mezzanine boards that have only static configuration parameters to ignore that connector.

# 3.3.3 The Trigger/Clock Fan-Out Back-Plane

The Trigger/Clock output will be fed through 6U fan-out boards which will be mounted from the back side of the 9U VME crate. The P2 VSB back-plane signals will be used for that purpose. All signals at this back-plane are 5V TTL signals. The choice of the VSB back-plane standard allows the use of this back-plane if more than one fan-out module is required per Trigger/Clock driver module. In this case, the VSB back-plane will be mounted at the back side of the VME P2 back-plane. Depending on the depth of the VSB back-plane, up to 8 fan-out boards can be driven by a single Trigger/Clock driver. The pin definition of the Trigger/Clock VSB back-plane is defined in Table 13.

The back side of the 9U VME board will have card guides supporting the 6U fan-out modules. These modules will sit behind the VME P2 and P3 back-plane. The fan-out boards have to support hot insertion because all Trigger/Clock driver modules will be in one crate, and a power cycle of that crate will affect the whole experiment. The connectors on the back side of the VME P2 or VSB back plane are of male type. Bent pins may cause shorts, which are dangerous especially if power pins are involved. Therefore the power of the VME P2 and VSB back-plane will be decoupled from the P1 and P3 back-plane. The

TABLE 11. The TCD PMC mezzanine card pin assignment

| pin# | signal name   | signal name     | pin# | pin# | signal name  | signal name | pin# |

|------|---------------|-----------------|------|------|--------------|-------------|------|

| 1    | detectorID[0] | -12V            | 2    | 1    | +12V         | C0BUSY      | 2    |

| 3    | GND           | detectorID[1]   | 4    | 3    | C2BUSY       | C1BUSY      | 4    |

| 5    | trig.CMDi[0]  | trig.CMDi[1]    | 6    | 5    | C3BUSY       | GND         | 6    |

| 7    | reserved,nc   | +5V             | 8    | 7    | GND          | COSTATUS    | 8    |

| 9    | trig.CMDi[2]  | trig.CMDi[3]    | 10   | 9    | C2STATUS     | C1STATUS    | 10   |

| 11   | GND           | detector select | 12   | 11   | reserved,nc  | reserved,nc | 12   |

| 13   | RHIC stb      | GND             | 14   | 13   | dly RHIC stb | reserved,nc | 14   |

| 15   | GND           | detector busy   | 16   | 15   | reserved,nc  | reserved,nc | 16   |

| 17   | trig.CMDo[0]  | +5V             | 18   | 17   | CE#          | GND         | 18   |

| 19   | reserved,nc   | trig.CMDo[1]    | 20   | 19   | OE#          | WE#         | 20   |

| 21   | trig.CMDi[2]  | trig.CMDo[3]    | 22   | 21   | GND          | CD[0]       | 22   |

| 23   | control[0]    | GND             | 24   | 23   | CD[1]        | reserved,nc | 24   |

| 25   | GND           | control[1]      | 26   | 25   | CD[2]        | CD[3]       | 26   |

| 27   | control[2]    | detectorID[3]   | 28   | 27   | reserved,nc  | CD[4]       | 28   |

| 29   | detectorID[2] | +5V             | 30   | 29   | CD[5]        | GND         | 30   |

| 31   | reserved,nc   | detectorID[5]   | 32   | 31   | CD[6]        | CD[7]       | 32   |

| 33   | detectorID[4] | GND             | 34   | 33   | GND          | CA[0]       | 34   |

| 35   | GND           | detectorCLK1    | 36   | 35   | CA[1]        | reserved,nc | 36   |

| 37   | detectorCLK2  | +5V             | 38   | 37   | GND          | CA[2]       | 38   |

| 39   | GMD           | RESET#          | 40   | 39   | CA[3]        | GND         | 40   |

| 41   | trig.WD[0]    | trig.WD[1]      | 42   | 41   | reserved, nc | CA[4]       | 42   |

| 43   | trig.WD[2]    | GND             | 44   | 43   | CA[5]        | GND         | 44   |

| 45   | reserved,nc   | trig.WD[3]      | 46   | 45   | CA[6]        | CA[7]       | 46   |

| 47   | trig.WD[4]    | trig.WD[5]      | 48   | 47   | CA[8]        | CA[9]       | 48   |

| 49   | trig.WD[6]    | +5V             | 50   | 49   | CA[10]       | reserved,nc | 50   |

| 51   | GND           | trig.WD[7]      | 52   | 51   | CA[11]       | CA[12]      | 52   |

| 53   | trig.WD[8]    | trig.WD[9]      | 54   | 53   | reserved,nc  | CA[13]      | 54   |

| 55   | trig.WD[10]   | GND             | 56   | 55   | CA[14]       | GND         | 56   |

| 57   | reserved,nc   | trig.WD[11]     | 58   | 57   | CA[15]       | CA[16]      | 58   |

| 59   | trig.WD[12]   | trig.WD[13]     | 60   | 59   | GND          | CA[17]      | 60   |

| 61   | trig.WD[14]   | +5V             | 62   | 61   | CA[18]       | reserved,nc | 62   |

| 63   | GND           | trig.WD[15]     | 64   | 63   | GND          | C3STATUS    | 64   |

# 3.3.2 The Trigger/Clock Mezzanine

All detector specific clock and trigger signals and functions have to be produced on this board. The development of this mezzanine board is the responsibility of each detector group. The physical board geometry and connectors are compliant with the IEEE P1386 Common Mezzanine Card Family (CMC) standard. The Trigger/Clock Mezzanine will be a double width, standard CMC board (149x149mm). It will have front-panel access as specified in IEEE P1386.

<u>Note:</u> The CMC standard was used to simplify the definition of the mezzanine board and connectors. The mezzanine board does not have to comply with all features of the P1386 standard. In fact, the following deviations will be implemented in order to simplify the design:

- The BUSMODE# coding and V(I/O) pins are not used and will be ignored.

- The P13 connector will have the pin assignment of the P12 connector. The P12 and P14 connector will not be implemented. The P21 and P23 connectors will have only the power and ground pins connected as in Table 11. P22 and P24 will not be implemented. These changes to the P1386 standard allow to completely omit the second connector row of the standard and still ensure mechanical stability of the mezzanine board.

TABLE 10. The signal groups on the CMC mezzanine connector

O(6) detector ID (3 bits), subdetector ID (3 bits)

#### trigger backplane inputs

- I(3x1) RHIC strobe, delayed RHIC strobe, detector select

- O(1) detector BUSY

- I(4) optional detector BUSY input from fan-out modules

- I(4) optional detector STATUS input from fan-out modules

- I(4,16) trigger CMD in, trigger word

## trigger command serializer outputs

- O(2) distributed clocks (detector Clk1, detector Clk2)

- O(3) serializer control (force trigger token and DAQ CMD to zero etc.)

- O(4) trigger CMD out

## configuration inputs

- I(19) mezzanine address bus I/O(8) mezzanine data bus

- I(4) CE#, OE#, WE#, RESET#

The six bit detectorID field contains three subdetectorID bits (D0...D2). The subdetectorID bits are required because there may be more than one Trigger/Clock driver module for the given detector. The detector ID bits are statically set by the Trigger/Clock mezzanine board and will be used for the VME slave address decoding logic on the mother board. This allows kind of a geographic detector addressing within the VME framework.

TABLE 9. The Trigger backplane pin assignment

| pin | signal (P3)  | (P1)   | pin | signal (P3)   | (P1) |

|-----|--------------|--------|-----|---------------|------|

| A10 | RHIC_STB     | SYSCLK |     |               |      |

|     |              |        |     |               |      |

| A01 | TRG_EMC      | D00    | B30 | BSY_EMC       | IRQ1 |

| A02 | TRG_SVT      | D01    | B29 | BSY_SVT       | IRQ2 |

| A03 | TRG_TOF      | D02    | B28 | BSY_TOF       | IRQ3 |

| A04 | TRG_TPC      | D03    | B27 | BSY_TPC       | IRQ4 |

| A05 | TRG_XTPC     | D04    | B26 | BSY_XTPC      | IRQ5 |

| A06 | TRG_spare    | D05    | B25 | BSY_spare     | IRQ6 |

| A07 | TRG_spare    | D06    | B24 | BSY_spare     | IRQ7 |

| A08 | TRG_spare    | D07    | A20 | BSY_spare     | IACK |

|     |              |        |     |               |      |

| A23 | TRG_CMD[0]   | AM4    | B16 | DAQ_CMD[0]    | AM0  |

| C14 | TRG_CMD[1]   | AM5    | B17 | DAQ_CMD[1]    | AM1  |

| A24 | TRG_CMD[2]   | A07    | B18 | DAQ_CMD[2]    | AM2  |

| C24 | TRG_CMD[3]   | A14    | B19 | DAQ_CMD[3]    | AM3  |

|     |              |        |     |               |      |

| A30 | TRG_TOKEN[0] | A01    | C30 | TRG_TOKEN[6]  | A08  |

| A29 | TRG_TOKEN[1] | A02    | C29 | TRG_TOKEN[7]  | A09  |

| A28 | TRG_TOKEN[2] | A03    | C28 | TRG_TOKEN[8]  | A10  |

| A27 | TRG_TOKEN[3] | A04    | C27 | TRG_TOKEN[9]  | A11  |

| A26 | TRG_TOKEN[4] | A05    | C26 | TRG_TOKEN[10] | A12  |

| A25 | TRG_TOKEN[5] | A06    | C25 | TRG_TOKEN[11] | A13  |

|     |              |        |     |               |      |

| C23 | TRG_WORD[0]  | A15    | C01 | TRG_WORD[8]   | D08  |

| C22 | TRG_WORD[1]  | A16    | C02 | TRG_WORD[9]   | D09  |

| C21 | TRG_WORD[2]  | A17    | C03 | TRG_WORD[10]  | D10  |

| C20 | TRG_WORD[3]  | A18    | C04 | TRG_WORD[11]  | D11  |

| C19 | TRG_WORD[4]  | A19    | C05 | TRG_WORD[12]  | D12  |

| C18 | TRG_WORD[5]  | A20    | C06 | TRG_WORD[13]  | D13  |

| C17 | TRG_WORD[6]  | A21    | C07 | TRG_WORD[14]  | D14  |

| C16 | TRG_WORD[7]  | A22    | C08 | TRG_WORD[15]  | D15  |

|     |              |        |     |               |      |

# 3.3.1 The Trigger Back-Plane

The P3 bus of the Trigger/Clock Driver Module will be used to distribute the actual Trigger L0 TCU output signals (Trigger backplane).

TABLE 8. The logical signal groups distributed at the trigger back plane

| A(1)  | I | RHIC strobe                                                                         |

|-------|---|-------------------------------------------------------------------------------------|

| B (8) | О | individual detector BUSY signals (one bit per detector, open collector, low active) |

| C (8) | I | coincident detectors (one select bit per detector)                                  |

| D (4) | I | Trigger Command                                                                     |

| E(4)  | I | DAQ command                                                                         |

| F(12) | I | Trigger Token                                                                       |

| G(16) | I | Trigger Word                                                                        |

Note: items A through B form the 16 bit Trigger Action Word

All signals are latched with the rising edge of the RHIC strobe. The setup time is 10 ns, and the hold time is 5 ns.

The individual detector busy signals are required for special trigger generation. The time required to process a special trigger command is not deterministic; it may result in several special triggers to be sent to the front-end. Therefore the special trigger sequencer on the detector specific mezzanine board has to be able to assert the detector specific dead time signal.

The Trigger Action Word is split into three logical fields as indicated in the above table. Each detector (up to eight) has its own bit indicating if it is involved in the given trigger command. The trigger command and DAQ command are global for any given event.

The trigger token is distributed in case of a trigger command that results in a read-out.

The Trigger Word is the 16 bit field that describes the trigger for the given bunch crossing associated with an event.

There has to be a back-plane that distributes these trigger signals. Most elegant would be the use of an existing back-plane, avoiding the need of the design of a private back-plane. It is possible to use a VME P1 back-plane at P3 for this purpose. The P3 signal-pin assignment of the Trigger back plane is shown in Table 9.

# 3.3 Trigger/Clock Driver Module

The Trigger/Clock driver module is the root of the Trigger/Clock distribution tree. Its major components are sketched in figure 1. The Trigger/Clock driver module will be implemented as a 9U VME board. The use of this widely accepted standard bus allows easy configuration access using only standard components and interface chips. The Trigger/Clock Driver Module will be identical for all detector systems. However it will host a detector specific mezzanine board that implements all the detector specific logic required to produce the clock signals and special trigger command sequences.

Therefore, there are four major components on the Trigger/Clock Driver Module: the VME slave interface, the trigger decode logic, the detector specific mezzanine board and the RHIC strobe delay logic. The VME slave interface allows configuration of all parameters and CSR registers of the board including the Trigger/Clock mezzanine board. The detector specific phase setting of the RHIC strobe will be defined by CSR readable jumpers to avoid malfunction due to a configuration mistake. All TCD resources will be memory mapped into the sub-address space of the Driver Module. The decode logic decides if a given trigger command includes the given detector. The most important component of the Trigger/Clock Driver Module is the detector specific mezzanine board. It generates the detector specific clock signals and the special command sequences. The output of the mezzanine board is serialized and forwarded to the fan-out modules. These 6U modules will be plugged in at the back side of the P2/P3 back plane. The signals of the P2 VSB bus will be used for passing the Trigger/Clock signals. There is one programmable delay line unit. It defines the relative phase of the RHIC strobe, from which all further clocks are derived.

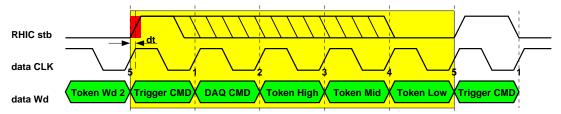

**FIGURE 2**: *The word sequence within one RHIC strobe period.*

receiver at its falling edge (in the middle of the eye pattern). Note the pulse length of the RHIC strobe as indicated in Figure 2 is for illustration only. The pulse length can range from 10ns to 90ns. Or in other words only the leading edge of the RHIC strobe may be used as timing reference.

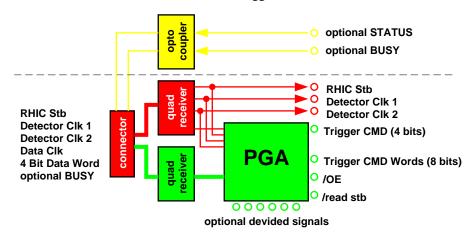

The Trigger/Clock receiver can be implemented in programmable logic. Figure 3 shows a sketch of one implementation. The FPGA output has an individual output enable to allow the receiver module to be connected to a global data bus. The Trigger CMD will be always driven with the last non zero trigger command.

**FIGURE 3**: *The Trigger/Clock receiver.*

Due to the small size of all components, the size of the Trigger/Clock receiver logic should not exceed 2 square inches, including the connector.

# 3.2 Trigger/Clock receiver module

Since the Trigger/Clock receiver interfaces to the front-end electronics boards of the STAR detectors, it needs to be defined precisely so that the designs of these systems can proceed.

After investigating various line driver/receiver chips<sup>1</sup> the AT&T 41 series chips (driver: 41MP; receiver: 41MF) were selected as suiting the requirement best. Their most interesting features are a very wide common mode rejection range (+/- 7V) and a very high bandwidth of up to 400Mb/sec for short cables.

There are five 4-bit entities that have to be distributed for each trigger (trigger CMD, DAQ CMD, Trigger token (12 bits)). Running the 4-bit word clock at 5 times the RHIC clock rate (well within the capabilities of the distribution tree) makes it possible to distribute the full trigger information within one RHIC strobe. Consequently, the Trigger/Clock distribution tree will be dead time free. The two last optional signals (BUSY and STATUS) are returned as wired OR to the Trigger/Clock driver Module.

**TABLE 7.** *The Trigger/Clock connector pinout:*

| Pin | Signal                    | Polarity | Pin | Signal                    | Polarity |

|-----|---------------------------|----------|-----|---------------------------|----------|

| 1   | RHIC strobe               | +        | 2   | RHIC strobe               | -        |

| 3   | D0                        | +        | 4   | D0                        | -        |

| 5   | D1                        | +        | 6   | D1                        | -        |

| 7   | D2                        | +        | 8   | D2                        | -        |

| 9   | D3                        | +        | 10  | D3                        | -        |

| 11  | data clock (5•RHICclk)    | +        | 12  | data clock (5•RHICclk)    | -        |

| 13  | detector clock 1          | +        | 14  | detector clock 1          | -        |

| 15  | detector clock 2          | +        | 16  | detector clock 2          | -        |

| 17  | optional BUSY feed back   | +        | 18  | optional BUSY feed back   | -        |

| 19  | optional STATUS feed back | +        | 20  | optional STATUS feed back | -        |

The actual 4 bit word sequence within one RHIC strobe period is sketched in Figure 2. The corresponding signals are underlined in light grey. The rising edge (dark) of the RHIC strobe defines the timing reference. The Trigger command is the most important word and needs to be available early. It is strobed out simultaneously to the rising edge of the RHIC strobe. The other words follow and are buffered in the Trigger/Clock receiver.

The data clock skew of the data clock with respect to the RHIC strobe (as indicated as *dt* in Figure 2) is limited to the specifications stated in paragraph 2.1 on page 4, thus making it also available as stable clock signal for use on the receiver end. The Trigger command nibbles are strobed out at the rising edge of the data clock and shall be latched in by the

<sup>1.</sup> These tests were carried out by A. Alyuschin, and M. Alyuschin, F. Bieser and S. Klein

#### Implementation

However all TOF front-end boards need to know of any triggers involving TOF. Consequently there is still a requirement for a Trigger/Clock distribution to the TOF front-end systems.

It is planned to distribute additional detector specific clock signals. The system design could be very simple if these clocks are produced at one well defined place and distributed to the front-end through the trigger clock distribution tree. Two independent detector specific clock signals are sufficient.

**TABLE 6.** The detector specific clocks required:

detector clock signal 1 clock signal 2 TPC: SCA clock #1 (~10 MHz variable) SCA clock #2 (~10 MHz variable) SVT: 3•RHICclk (SCA write clock) 1/3•RHICclk (SCA read clock) EMC: 4...5•RHICclk ToF: 4•RHICclk xTPC: CTBMWC

**Note:** The various requirements were only listed here in order to sustain the maximum clock rates stated in 2.7. This number defines the requirement for the transceivers of the Trigger/Clock distribution tree. The actual clock rate distributed through the Trigger/Clock distribution tree does not matter at all as long as it does not exceed this maximum. The table above indicates that roughly 50MHz are sufficient for all STAR detector systems.

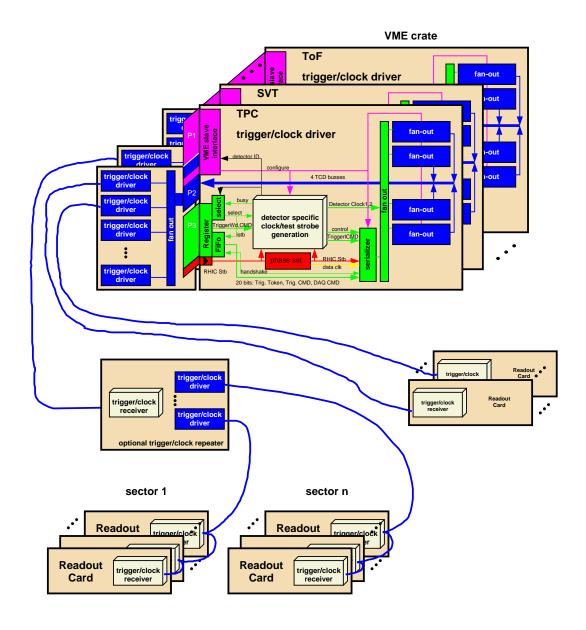

**FIGURE 1**: *The major components of the Trigger/Clock distribution tree.*

# 3. Implementation

### 3.1 Overview

Figure 1 shows a sketch of the currently envisioned Trigger/Clock distribution tree. There will be one or several root driver modules for each individual detector. All root modules will sit in a VME crate and receive the 96 trigger bits and RHIC strobe at the back plane. Each trigger root module will have a detector specific mezzanine board to generate the required detector specific clock signals.

The trigger distribution tree may be implemented in two different ways: point-to-point with length adjusted cables and multi drop. For example, for the TPC a multi drop cable per sector may be sufficient. However this imposes that there may be a clock phase difference between the readout boards of a sector of as much as 5ns. Detectors that need the clock phase to be determined more accurately may have to use point-to-point links as indicated in Figure 1 for the case of the SVT.

There may be an optional second layer of boards, simple repeaters, that drive the cables to the individual readout boards. In case of the TPC, for example, there will be two of these repeaters on each end cap driving 12 individual sector cables. Any delay adjustments on these boards would be implemented with jumpers. There will be no way to configure these boards by software. However, the use of these repeaters is a pure implementation issue.

**TABLE 5.** The number of Trigger/Clock distribution cables per detector and end cap of STAR

(Note: the readout granularity of EMC and ShowerMax is not final; the numbers quoted are estimates for the detector + endcap)

**TPC:** 24 one cable per inner and outer sector using multi drop

**SVT:** 12 one cable per readout board

**EMC:** 60+24 **ShowerMax:** 60

**ToF:** 60 one cable per Receiver/Control Module

**xTPC:** currently not defined

CTB MWC

**Note:** Requirement 2.1 states a maximum incoherent jitter of 50 ps RMS for the clock distribution of the TOF system. This requirement is more difficult to satisfy than all the others since the Trigger detectors run in lock step with the RHIC clock and do not need distribution of any trigger or abort signals. The TOF time to pulse height converter stop signals requiring that low jitter will have to be implemented by the TOF crew and are considered outside the scope of the Trigger/Clock distribution tree.

# 2.11 Support of detector specific clock signals

## Requirement:

For each STAR subdetector there has to be provision to generate and distribute two detector specific clock signals.

## Justification

The state machines and digitizers of the various front-end boards need usually some common detector specific clock signals. It is ergonomic to generate those in one place and distribute them together with the RHIC strobe.

## Note:

This feature will be implemented using mezzanine cards, which are detector specific and plug onto the common TCD mother board. The mezzanine card will have front-panel access.

# 2.9 Accept individual front-end electronics busy and DAQ busy

## Requirement:

Accept one individual busy signal from each detector's front-end electronics and one corresponding DAQ front-end busy (no common dead time).

There is no requirement for a BUSY wired-or feed back tree from the TC front-end.

## Justification:

STAR does not have a common dead time. There is dead time created by the front-end electronics during digitization of an event or while clearing an event. Another source of dead time is the DAQ front-end if all available elasticity buffers are allocated. The trigger control unit will use the logical OR of these signals of a given detector as the detector busy input and if asserted prohibit any further triggers to the given detector.

#### Note:

The physical TCD busy input is a TTL signal, which is decoupled by an opto-coupler to avoid ground loops. The connector is LEMO with the isolated ground on the connector chassis. An active HIGH corresponds to BUSY status set. The TCD busy input is guaranteed to not source or sink more than 10mA.

# 2.10 Readout card buffer space requirement

## Requirement:

Each detector that runs at higher rates than the TPC (100/sec; 10 ms digitization time) is required to buffer its TPC related data. Fast detectors like EMC and TOF may send their data to DAQ only after a L2.

#### Justification:

This requirement allows the trigger system to issue new triggers to fast detectors before their TPC related data was completely read out. With this rule it is possible to clear a TPC event including EMC data after another non coincident EMC event is completely read out.

The interface between the front-end and DAQ becomes very simple, since an event will never be cleared after it was completely transmitted.

Requirements 13

# 2.7 Multi Drop

## Requirement:

Support Multi Drop - allow powering down one Trigger/Clock receiver in a multi drop chain without interfering with the rest of the tree.

## Justification:

Some detectors (TPC) will implement the Trigger/Clock distribution as a multi drop bus. This saves a lot of cable and cable space. However it may be required to power down an individual readout board. This condition must not interfere with the trigger and clock distribution of the other still running readout boards which are connected to the same branch.

# 2.8 Physical Signal Distribution

## Requirement:

The physical Trigger/Clock signal distribution requirements are:

- · differential, copper

- maximum cable length 30 m

- maximum ground potential difference (common mode suppression) 1 V

- · highest frequency distributed: five times RHIC clock

## Justification:

Given the number of Trigger/Clock distribution tree end nodes of about 1000, and given the moderate distance and clock rate, a fiber optics based system cannot be justified. The electrical requirements must be specified to allow the design of the Trigger/Clock distribution tree.

## 2.5 DAQ Command Word

## Requirement:

Distribute for every trigger a global 4 bit DAQ command word to all DAQ front end systems of all coincident detectors.

## Justification:

There are event attributes that require the same handling on the front-end electronics level but different handling of the raw data on the DAQ front-end level. For example, normal events, and baseline events (or scale-down events) that have to bypass the L3 filter, require the same handling on the readout boards. However, on the receiver boards their handling is significantly different. It is possible, in principle, to fetch this information from the Trigger-DAQ interface and distribute it to all DAQ front-end systems for each event. But considering that there are 144 receiver boards just for the TPC, this approach seems clumsy. A much cleaner method is to distribute a descriptive bit pattern to DAQ, together with the data that allows to disentangle different handling procedures in the front-end.

Four bits or 16 different commands are sufficient. The same DAQ command word is distributed to all coincident detectors. The meaning of the DAQ command words are not yet defined.

#### Note:

The DAQ Command Word will be produced together with the Trigger Command word in the trigger action word lookup table within the TCU.

# 2.6 Maximum Trigger distribution dead time

### Requirement:

The maximum time to distribute a complete trigger command is 5 RHIC strobes.

## Justification:

The time required to distribute a trigger or clear command affects the dead time and therefore the detector performance. Also, it defines the minimum time between two successive trigger pulse commands. There are no detector systems in STAR that require triggers or test strobes closer than 5 RHIC strobes back-to-back.

#### Note:

There will be no dead time associated with the Trigger/Clock distribution. It is be possible to distribute the whole 20 bit trigger information within one bunch crossing.

Requirements 11

# 2.4 Trigger Token

#### Requirement:

Generate a unique 12-bit trigger token for every trigger and distribute it with each trigger, accept and abort command.

## Justification:

The STAR detector consists of many independent sub-detector systems, with its own dead time. Any combination of detectors is possible for coincident triggers. The readout time of the various systems varies greatly. Therefore, it is possible that during the conversion of one detector another detector is already live and ready to take more data. The STAR trigger system supports triggers to fast detectors even if their previously coincident event with a slow detector is still being processed. Therefore, it is important to have a mechanism that allows to identify uniquely which event and detector any data buffer belongs to. In order to identify uniquely a data buffer with a given event, the trigger system will distribute a unique trigger token together with the trigger command itself. The L1/L2accept and abort commands identify the event with the trigger token as well.

One way to make the trigger token unique is to use enough bits to make sure that the same trigger token will never be used again. For example, a 64 bit bunch crossing number would satisfy this requirement. However, cost considerations require the number of bits transferred per trigger to be as small as possible. Another approach is to make sure that the same trigger token is not used again until the event is assembled. In this scenario the number of bits required for the trigger token is defined by the maximum number of outstanding triggers that are allowed by the data acquisition system. An upper limit for this number is defined by the highest accepted DAQ trigger rate (1000/sec) and the maximum DAQ latency (2s). Correspondingly, a 12 bit trigger token is sufficient. The trigger system will reuse a trigger token only if the corresponding event was readout and assembled by DAQ and the appropriate trigger structures were cleared by DAQ in the Trigger-DAQ interface (refer to the Trigger-DAQ interface specification).

#### Requirements

TOF: reserved - ignored XTPC: reserved - ignored

config

12: This is a housekeeping trigger. It has to be supported by all detector systems and returns geographic information of the front-end boards allowing automatic configuration of the experiment.

## **TABLE 4.** Group 3 Trigger Commands:

abort

13: This command aborts and clears an active event. Which event must be cleared is defined with the accompanying unique trigger token.

L1accept

14: This command informs the front-end that there is a level one (L1) accept of the event identified by the trigger token. It is useful for detectors that perform level two (L2) analysis on their data. The L1 accept will define the event to be available for this L2 analysis, preventing the L2 processors from wasting time on events that will be cleared by the trigger L1 logic.

L1accept commands may be issued in any order.

L2accept

15: This command informs the front-end that the event identified with the trigger token was accepted by the trigger system and that DAQ was informed about the existence of that event. Fast detectors like EMC and TOF use this command to start the transmission of the event to DAQ. After receipt of a L2accept command aborts for that event are impossible.

L2accept commands may be issued in any order.

Requirements 9

#### Requirements

SVT: executed as trigger0 but copy event also into local

buffer

EMC: reserved - executed as trigger0

TOF: reserved - executed as trigger0

XTPC: reserved - executed as trigger0

pulser<sub>n</sub> 8+n:

There are four different test strobe commands available that will be used to fire test pulses or to fire a laser for calibration and monitoring purposes

Note: The test pulse command produced by Trigger may be intercepted by the Trigger/Clock Driver module and result in a sequence of test pulse commands. This test pulse sequence will be protected by the detector dead time signal which will be asserted by the Trigger/Clock Driver module while performing that sequence. The Trigger/Clock Receiver modules can easily disentangle a pulser command that shall just fire the specified pulser or laser and the final test pulse command that requires also the readout because only the latter will be accompanied by a non zero trigger token.

pulser0 8:

TPC: electrical pulser, TPC charge injection SVT: electrical pulser - calibration pulser

EMC: electrical pulser - charge injection to PMT and Show-

erMax

TOF: reserved - ignored XTPC: electrical pulser

pulser1 9:

TPC: laser

SVT: electronics test pulser (not implemented in FEE)

EMC: LED/laser trigger

TOF: laser XTPC: laser

pulser2 10:

TPC: ground plane pulser

SVT: reserved - ignored

EMC: radioactive source

TOF: reserved - ignored

XTPC: reserved - ignored

pulser3 11:

TPC: buffered readout - reproduce event stored by trigger3

command

SVT: buffered readout - reproduce event stored by trigger3

command

EMC: reserved - ignored

## Requirements

trigger3

7:

TPC:

# TABLE 2. Group 1 Trigger Commands:

| no-trigger           | 0:   | This is the idle link.                                                               | default symbol that will be transferred in the case of an                                                                                                                                        |  |  |

|----------------------|------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                      |      | The Trigge teed to be z                                                              | r Token following the <i>no-trigger</i> command is guarantero                                                                                                                                    |  |  |

| clear                | 1:   | This comm                                                                            | and clears redundancy counters on the readout boards.                                                                                                                                            |  |  |

|                      |      | RHIC strob<br>with the ray                                                           | at boards will have redundant counters counting the be. The value of these counters will be shipped together w data allowing cross checks that each system received same number of clock pulses. |  |  |

| master-reset         | 2:   | This comm logic.                                                                     | This command will perform a general reset of the whole front-end                                                                                                                                 |  |  |

| spare                | 3:   | reserved                                                                             |                                                                                                                                                                                                  |  |  |

|                      |      | _                                                                                    | igger Commands: the following tables the Electromagnetic Calorimeter and the                                                                                                                     |  |  |

|                      |      | ax detector                                                                          | ·                                                                                                                                                                                                |  |  |

|                      |      |                                                                                      |                                                                                                                                                                                                  |  |  |

| trigger <sub>n</sub> | 4+n: |                                                                                      | There are four trigger commands available allowing four different kinds of readout in the front-end.                                                                                             |  |  |

| trigger0             | 4:   | This is the default physics readout and has to be supported by all detector systems. |                                                                                                                                                                                                  |  |  |

|                      |      | TPC:                                                                                 | physics readout                                                                                                                                                                                  |  |  |

|                      |      | SVT:                                                                                 | physics readout                                                                                                                                                                                  |  |  |

|                      |      | EMC:                                                                                 | Electron Trigger (EMC/TPC coincidence)                                                                                                                                                           |  |  |

|                      |      | TOF:                                                                                 | physics readout                                                                                                                                                                                  |  |  |

|                      |      | XTPC:                                                                                | complete physics readout                                                                                                                                                                         |  |  |

| trigger1             | 5:   |                                                                                      |                                                                                                                                                                                                  |  |  |

|                      |      | TPC:                                                                                 | reserved - executed as trigger0                                                                                                                                                                  |  |  |

|                      |      | SVT:                                                                                 | reserved - executed as trigger0                                                                                                                                                                  |  |  |

|                      |      | EMC:                                                                                 | Isospin readout (assumes EMC/TOF coincidence)                                                                                                                                                    |  |  |

|                      |      | TOF:                                                                                 | reserved - executed as trigger0                                                                                                                                                                  |  |  |

|                      |      | XTPC:                                                                                | reserved - executed as trigger0                                                                                                                                                                  |  |  |

| trigger2             | 6:   |                                                                                      |                                                                                                                                                                                                  |  |  |

|                      |      | TPC:                                                                                 | reserved - executed as trigger0                                                                                                                                                                  |  |  |

|                      |      | SVT:                                                                                 | reserved - executed as trigger0                                                                                                                                                                  |  |  |

|                      |      | EMC:                                                                                 | reserved - executed as trigger0                                                                                                                                                                  |  |  |

|                      |      | TOF:                                                                                 | reserved - executed as trigger0                                                                                                                                                                  |  |  |

|                      |      | XTPC:                                                                                | reserved - executed as trigger0                                                                                                                                                                  |  |  |

Requirements 7

buffer

executed as trigger0 but copy event also into local

# 2.3 Trigger Command Word

Requirement:

Distribute a global 4 bit trigger command word as defined below.

Justification:

Each readout board needs to know for a given RHIC strobe if certain actions are required.

Generally, the number of bits needed to be communicated per trigger or abort should be kept as small as possible because it relates to either transmission speed or the number of signals of the trigger distribution cable. Both affect the cost of the system. Sixteen different trigger commands are sufficient. This allows to encode them into a 4 bit binary word. To define a good timing reference these trigger command words must be sampled at the rising edge of the RHIC clock.

**TABLE 1.** There are three classes of Trigger Command Words:

- 1 Commands that are not readout related

- 2 Commands that are readout related and require an event to be produced in the front-end

- 3 Commands that are readout related and accompanied by a valid trigger token but that do not result in any readout.

The first group contains commands that have to be distributed synchronously to the RHIC strobe and are not related to readout. These commands are broadcast to the detectors. The trigger token and DAQ command word that are distributed together with these trigger command words will be forced to zero. These commands will be distributed independent of the busy status of the detector.

The second group requires Trigger to produce and reserve a unique trigger token different from zero that is distributed together with the Trigger Command. Depending upon the Trigger Command, it has to inform DAQ about the event as specified in the Trigger-DAQ interface.

# 2.2 Phase Adjustability

#### Requirement:

The phase of the RHIC strobe and all affiliated signals has to be adjustable in steps of no more than 12 ns over a dynamic range of four RHIC strobes. There is no need for adjustment of the individual trigger/clock signals on the TCD mother board. There is one phase shifter per TCD mother board. The phase setting is defined by jumpers.

## Justification

Because all TCD signals are derived from the phase shifted RHIC clock multiple clock masters with possibly different phases would require multiple mezzanine cards on the TCD mother board. If a subdetector requires multiple phase adjustment it is required to use one TCD mother board for each independent phase.

It is essential that the RHIC strobe that is delivered from the accelerator is a free running clock that does not have any strobes missing for example for empty bunches.

The phase configuration is implemented using jumpers in order to avoid accidental changes due to software bugs. The setting, however, will be software readable.

It is essential that the RHIC strobe that is delivered from the accelerator is a free running clock that does not have any strobes missing for example for empty bunches.

## Note:

The Trigger/Clock Driver (TCD) will perform a coarse adjustment in steps of 12ns by delaying the RHIC strobe. All other signals are derived from that phase shifted RHIC strobe. The phase of the detector specific clock signals can be defined on the mezzanine board.

If finer adjustment of any of the clock signals is required it will be implemented on the front-end and is out of the scope of this document. The simplest approach would be to cut all cables to equal length and tolerate the cable skew wherever possible.

Requirements 5

# 2. Requirements

## 2.1 Clock Distribution

#### Requirement:

Distribute the RHIC strobe as the central heart beat to all detector systems. The timing jitter with respect to the RHIC strobe input to the trigger distribution tree is limited to 1ns RMS.

#### Justification:

The RHIC strobe (~110 ns clock period) defines the interaction time and can thus serve as the heart beat of the whole detector. It will be used as timing reference for all state transitions in the detector system.

There are three parameters relevant for the Trigger/Clock distribution tree:

- 1) <u>phase:</u> the average phase difference at the end points of the Trigger/Clock distribution tree (the readout boards) due to different propagation delays and cable lengths

- 2) <u>coherent jitter:</u> the phase of all Trigger/Clock distribution receivers varies in phase with respect to the RHIC strobe on an event-by-event basis.

- 3) <u>incoherent jitter:</u> the phase of all trigger /clock distribution receivers varies with respect to each other within an event. This number defines the timing resolution possible with signals derived from the Trigger/Clock distribution tree.

The maximum acceptable phase and jitter is defined by the detector requirements:

|       | phase | coherent jitter | incoherent jitter                |

|-------|-------|-----------------|----------------------------------|

| TPC:  | 5 ns  | 5 ns (RMS)      | 1 ns (RMS)                       |

| SVT:  | 12 ns | 1 ns (RMS)      | 1 ns (RMS)                       |

| EMC:  | 2 ns  | 2 ns (RMS)      | 2 ns (RMS)                       |

| ToF:  | 2 ns  | 2 ns (RMS)      | 2 ns (RMS) (excluding TDC logic) |

| xTPC: | 5 ns  | 5 ns (RMS)      | 5 ns (RMS)                       |

| TRIG: | 1 ns  | 1 ns (RMS)      | 25 ps (RMS)                      |

# 1. Introduction

This document describes the interfaces between the trigger system and the front-end electronics systems of the various detectors of STAR. The most important interface is the trigger and clock distribution tree. This tree delivers the actual triggers and clears to all frontend systems. It also distributes clocks such as the RHIC clock.

*Introduction* 3

# Sign-Off Page

The STAR management and group leaders agree to the definition of the interface between the STAR trigger system and the front-end systems as defined in this document. Further changes to this Trigger/Clock distribution tree will require the written agreement of all involved parties.

Jay Marx

Richard Jared

Rene Bellwied

Fred Bieser

Billy Bonner

Tom Cormier

Henry Crawford

Volker Eckhardt

Spencer Klein

Mike LeVine

# **Change Log**

| November 94 | V1.0  | First version accepted                             |

|-------------|-------|----------------------------------------------------|

| June 95     | V1.0a | Fiber commands clarified                           |

| February 96 | V1.1  | Document converted to FrameMaker, TCD clock phases |

|             |       | clarified                                          |

| April 96    | V1.2  | Sign-off Version                                   |

|             |       |                                                    |

# **Trigger/Clock Distribution Tree**

# **Requirement Document**

Version 1.2 - April 10, 1996

<u>V.Lindenstruth</u>, R. Bellwied, F. Bieser, B. Bonner, M. Botlo, J. Cannon, H. Crawford, L. Greiner, G. Hoffmann, R. Jared, S. Klein, M. LeVine, T. Noggle, E. Platner, J. Schambach, D. Underwood